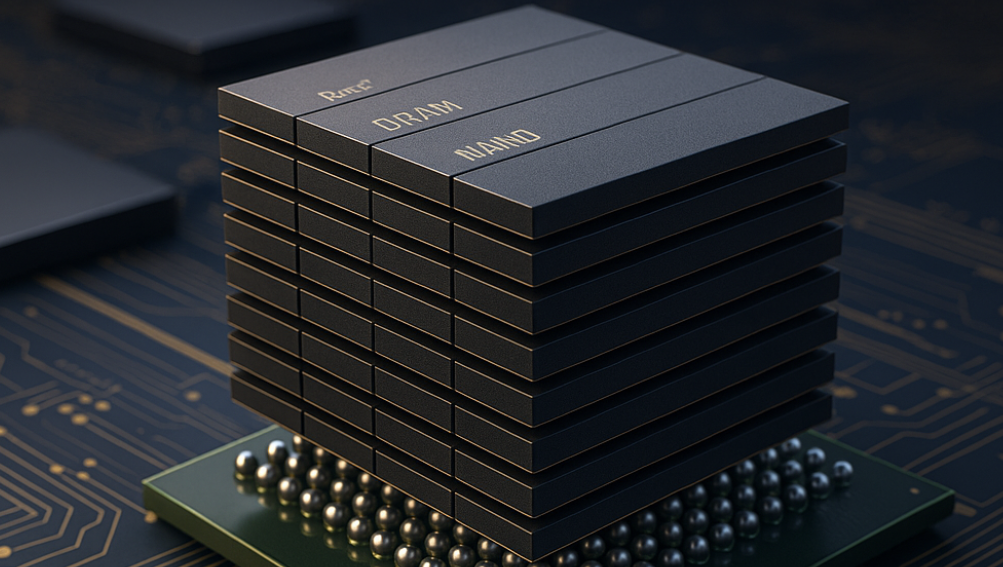

近日,据韩国“电子新闻”报道,SK海力士正研发一种新型高带宽存储(High Bandwidth Storage,简称HBS)架构,通过将多达16层DRAM与NAND芯片垂直堆叠,实现更高的数据吞吐与能效比。这一新技术,或许将提升智能手机和平板电脑的AI算力。

“堆叠”出的高带宽

据多方报道,SK 海力士计划采用一种名为垂直导线扇出(VFO)的封装工艺,将最多 16 层 DRAM 与 NAND 芯片垂直堆叠,从而显著提升数据处理速度。VFO技术最早就是由SK海力士在2023年展示的,AI时代的到来让这种技术有了用武之地。

传统电子产品的存储架构一般都会将DRAM和NAND分离使用,分别负责运算缓存与数据存储。VFO 取代了传统的弯曲导线连接方式,既缩短了布线距离,又减少信号损耗与延迟,并能支持更多 I/O 通道,使整体数据处理性能大幅提升。而HBS通过封装融合两者,在更紧凑的物理空间内实现高速协同。

而与 HBM 相比,HBS 无需采用硅通孔(TSV)工艺,意味着芯片制造不必穿孔,成本更低、良率更高。

从公开信息看,这一新架构的目标是“提升手机AI计算性能”。在当下,手机AI的算力瓶颈往往出现在内存带宽上——模型越大,访存越频繁,数据吞吐越成为瓶颈。HBS将DRAM高速缓存与NAND存储结合,能让AI任务在本地以更低功耗完成更多推理操作。

这对于AI摄影、实时翻译、语音识别等需要本地AI计算的场景意义重大。用户体验的提升将不仅体现在速度上,更在于延迟减少、续航改善和AI功能的响应即时性。

更关键的是,SK海力士此举也是对未来AI手机架构的提前布局。当前,苹果、高通、联发科均在强化“端侧AI”,但它们在芯片算力上已逼近物理极限。HBS这种“存储加速”路径,为AI算力增长开辟了第二条跑道。

HBM之后的下一个故事

过去两年,SK海力士凭借HBM3E在高性能计算领域赢得了与英伟达的深度合作。如今,它再次在HBS发力,表明其不满足于数据中心市场的成功,而希望在消费电子与AI端侧继续扩张。

与HBM相比,HBS的带宽虽低,但成本与能耗更适合移动端。它是一种面向端侧市场的高带宽存储形态,有望将HBM的理念延伸至消费领域。

从技术谱系上看,HBS可视作HBM与UFS之间的中间形态:

业内普遍认为,存储正成为AI时代的“第二核心”。GPU计算能力的提升已经遇到能耗瓶颈,而数据访问效率正成为新的限制因素。在这一趋势下,SK海力士的新技术体现出其对未来算力逻辑的洞察:带宽就是算力,数据流即能效。

未来,当AI模型持续扩大,用户对隐私与延迟的要求提高,本地AI推理将成为主流。届时,HBS的价值将不仅在于速度,更在于让“AI更靠近用户”。

当16层堆叠成为现实,数据世界的“高速公路”将更宽,AI的响应将更快,而手机,或许将迎来真正意义上的“本地智能时代”。